делител таймери

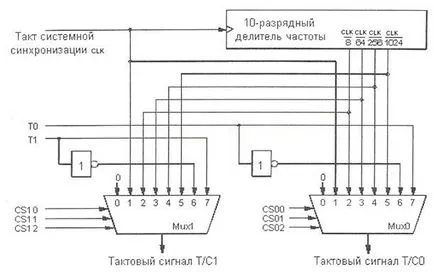

Както бе споменато по-рано, всеки таймер микроконтролер може да работи с два различни източника на тактови импулси. Или, че външните импулси или импулси, генерирани от вътрешния вериги на микроконтролера. Независимо от източника аудио сигнал е бил избран преди таймера да получите на входа на този сигнал минава делител верига. Честотния делител е проектиран да разшири обхвата на генерирана честота и продължителност таймер. Всеки чип има AVR-структура кръг делител за таймер / броячите. Опростена схема на едно изпълнение на делител е показано на фиг. 5.1.

Както се вижда от горните схеми са интегрирани в микроконтролера 10 и стъпиха разделителните мултиплексори провеждане връзка разделител изход, съответстващ на входните броячите.

С подвижен разделител изходни сигнали SLK / 8, CLK / 64, CLK / 256 и CLK / 1024. В схема задържане верига, чрез който външните импулси T0 и Т1 може да се стигне до входа на таймера.

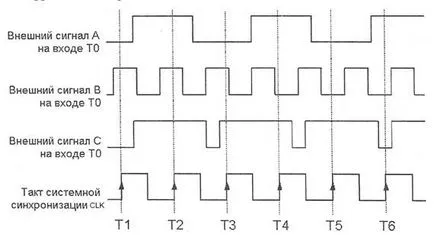

При работа "борба", като активен фронт от мултиплексор може да бъде избран nispodayuschy или нарастващ фронт на външен импулс на T0 и Т1 входове. В този режим външен T0 сигнал (като Т1) синхронизирано с системния часовник такт SLK вътрешния кристален осцилатор. За тази цел на външната сигнал се проверява по време на всеки нарастващ фронт SLK (фигура 5.2).

Фиг. 5.2 показва различни сигнали, които са синхронизирани сигнал CLK, така че е необходимо да се отбележи, че само сигнал е синхронизиран без загуба на информация. Това трябва да се вземат предвид при избора на работа MCU.

По този начин, в CSn0 на нивото на запис, CSnl, CSn2 различни стойности могат да бъдат избрани от експлоатация осем режима делител. В зависимост от избрания режим, към схема сигнал изход може да дойде от един от разделител изход десет цифри, директен сигнал от генератора на часовник или ниво нула логика (D0 вход). В последния случай, сигналът на входа таймер липсва, и неговата работа е спряно.

Има clkI / O стойност, определена от честотата на процесора часовник.

Така делител верига дава следната осем различни изпълнения образуването на броими импулси:

· 0 - липса на импулси;

· 1 - "таймер", директния сигнал от вътрешния осцилатор;

· 2. 5 - "таймер", един от сигналите от делител;

· 6 - "брояч" обратен сигнал от външен източник (активно

· 7 - "борба", външен сигнал линия (активен нараства

Схемата, показана на Фиг. 5.1 не е стандарт за всички микроколона контролер AVR серия. Той отразява общия принцип на предварителните разделители. Различните модели се направи малко по-различно.

Както вече споменахме, методът се определя от бита тактовата CSn2: 0 (Clock изберете), разположени в контрола регистрирате TCCRnB.