Адер и половина-ехидна

компютърни основи Logic

Процесор аритметично логическо устройство (ALU), трябва да съдържа в състава си елементи като разширители. Тези схеми позволяват да добавите двоични числа.

Как добавянето на? Да предположим, че искате да се определят двоични числа 1001 и 0011. Първо добави значителни бита (последната цифра): 1 + 1 = 10. Т.е. в най-маловажният бит е 0, а единица - се прехвърля към MSB. Следваща: 0 + 1 + 1 (от прехвърляне) = 10, т.е. Това е написано в тази цифра 0 отново, а устройството ще отидат в MSB. В третия етап: 0 + 0 + 1 (чрез прехвърляне) = 1. В резултат на сумата е равно на 1,100.

полу-ехидна

Сега ние няма да се обърне внимание на трансфера на предишното освобождаване от отговорност, и помислим колко сума от текущата изхвърлянето. Ако не са дадени две единици или две нули, количеството на разряден ток е равен на 0. Ако едно от двете условия е равен на една, след това сумата е равен на единица. Вземете тези резултати е възможно с помощта на изключителната-ИЛИ порта.

единици носят до случва последващо изтичане, ако двете условия са равни на една. И това е реализуема клапан I.

След прибавяне в рамките на един разряд (без възможни единици взрив от LSB) може да се реализира чрез схема показано по-долу, който се нарича половин разширител. В два полу-ехидна вход (за изражение) и два изхода (за сумата енд Кери). Диаграмата показва половин разширител, състояща се от изключителна ИЛИ порта и I.

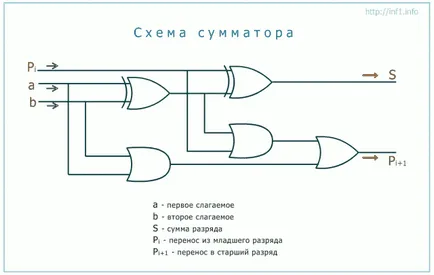

В контраст с ехидна половината ехидна дава възможност за прехвърляне на предишното освобождаване от отговорност, така че е не два, а три входа.

За да се даде възможност за прехвърляне на сметки за проста схема. Всъщност, оказва се, състоящ се от два полу-усойница.

Помислете за един от случаите. Изисква сгънати 0 и 1, и 1 на прехвърлянето. Ние първо да се определи размерът на разряден ток. Съдейки лявата верига XOR, който включва а и б, изходът е един. В следващия XOR вече включва две единици. Следователно, количеството ще бъде равна на 0.

Сега погледнете какво се случва с трансфера. В един и врата са 0 и 1 (а и б). Получаваме 0. Във втория клапан (вдясно) две единици отиват, давайки 1. преминаването през ИЛИ порта и земята от първия блок, а вторият ни дава 1.

Потвърждаване на действието на веригата чрез добавяне 0 + 1 + 1 = 10. Т.е. 0 остава в разряден ток, а устройството превключва на старши. Вследствие на логическия блок работи правилно.

Работата на веригата при всички възможни стойности за въвеждане може да бъде описан от следния истина масата.

Изображенията, използвани в статията

Таблицата с истината за ехидна

А спусъка като елемент с памет. Схема RS-флоп

компютърни основи Logic

Памет (устройство за съхранение на данни и инструкции) е важна част от един компютър. Може да се каже, че тя е неговата, и определя дали устройството компютри не си спомня, че не е компютър.

единица елементарна компютърна памет е малко. Следователно, устройството е необходимо, което може да бъде в две състояния, т.е. съхраняване на една или на нула. Също така, това устройство трябва да бъде в състояние бързо да превключвате от едно състояние в друго под влиянието на външната страна, което го прави възможно да се промени информацията. На последно място, устройството трябва да бъде в състояние да определи неговото състояние, т.е. поддават на информация за състоянието им.

Устройство може да запомни, съхранява и даде възможност да прочетете информацията, е спусъка. Той е изобретен в началото на XX век, Bonch-Bruevich.

Разнообразие от тригери е много голям. Най-простият от тези така наречени RS-тригер. който е сглобен от две врати. Клапани обикновено се използват NOR или NAND.