Прекъсване контролер APIC (за напреднали програмируем контролер прекъсване) - информатика,

Прекъсване контролер 5. APIC (Advanced Programmable Interrupt Controller)

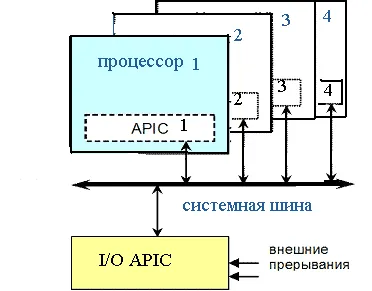

Система APIC (фиг.3). Състои се от местните контролери, монтирани в процесорите, както и контролер на прекъсване (един или повече) на I / O устройства. Задачата на всяка местна контролер (Local APIC) - излъчване на съобщения, получени в сигнали, които причиняват всички хардуерни прекъсва своя процесор - маскирани (INTR), nonmaskable (НИМ) и прекъсването системна услуга (SMI). В допълнение, на местната APIC позволи всеки процесор за генериране на прекъсване на други процесори. Местната контролерът разполага и с вътрешен интервал таймер, който позволява да се генерира прекъсване чрез програмируем интервал от време.

Фигура 3. Взаимодействие и вградени APIC I / O APIC SBus

Прекъсване контролер от вход / изход (I / O APIC) в режим на многопроцесорни е отговорен за разпространението на прекъсванията между процесори, които могат да бъдат използвани за статично или динамично разпределение. В случай на статично разпределение за всяко прекъсване число показва броя на процесор, който го обслужва. В случай на динамично разпределение на всяка приоритетна прекъсне за малко в момента процесора. Този контролер е отговорен за разпространение на сигнали на системни събития (NMI, INIT, SMI) и interprocessor прекъсва.

Вграден програмируем процесор APIC прекъсване контролер увеличава броя на въведената преди функции прекъсват контролер. Вграден APIC регистър за прекъсване източници в рамките на процесор (например, регулиране на температурата за единица) или от външен контролер и прекъсват предаването им процесор ядро за обработка. Особено важна роля се възлага на вградените многопроцесорни системи APIC където APIC получава и генерира съобщения за интер-процесор прекъсване (IPI - InterProcessor прекъсвания). Такива съобщения могат да се използват за разпространение на прекъсване на обработката сред процесори или да изпълняват функции на системата (на първоначалното зареждане, планиране на задачи, и т.н.). Всички процесори в многопроцесорни системи, получаващи сигнали от вход INTR # на (maskable хардуерно прекъсване). АКО малко в знамената регистрират позволява да блокирате (маска) боравенето с такива прекъсвания. Прекъсването на сигнали, постъпващи НИМ #, хардуерни Прекъсването се демаскира НИМ не блокира флаг IF. Както вече знаете, докато програмата се изпълнява - НИМ манипулатор, процесорът забранява получаването на НИМ, преди да изпълни IRET инструкции да се избегне едновременното обработване на множество НИМ. Структурата построен APIC е архитектурен подмножество на Intel 82489 чип прекъсване контролер.

Застроена APIC прави разлика между следните прекъсва:

1. От местните вътрешни устройства. прекъсване искане сигнал се получава от устройството, свързан директно към LINT0 на сигнали и LINT1 (например, preryvaniytipa контролер 8259A).

2. От външно устройство. заявка за прекъсване на сигнала от устройство, свързано към системния контролер прекъсване.

3.Mezhprotsessornye (IPI). В многопроцесорни системи, един процесор може да се прекъсне един от IPI съобщения.

4. От таймера APIC. Застроена APIC съдържа таймер, който може да бъде програмиран да генерира прекъсване на определен момент.

5. От изпълнението на таймера монитор. Съвременните процесори съдържат орган за наблюдение на изпълнението. Това устройство може да се програмира така, че свързаната с таймера, когато на определен референтен да генерира прекъсване.

6. От сензора за температура. Съвременните процесори съдържат вграден температурен контрол единица, която може да бъде програмиран да генерира прекъсва.

7. Вътрешен APIC грешка. Застроена APIC може да генерира прекъсване, когато възникне състояние на вътрешна грешка (например, когато се опитвате да получите достъп до несъществуваща регистър APIC).

Позоваването 1, 4, 5, 6, 7, се считат за местни източници на прекъсва обслужвани APIC специален набор от регистри нареченото локално маса вектор (LVT - местно маса вектор). Две други източници се обработват от механизма на APIC съобщение. Тези съобщения, тъй Pentium 4 процесор се предават на системната шина, така контролера прекъсване е свързан директно към конвенционална система интерфейс (например, PCI автобус). Вграденият процесор APIC открива при използване на инструкцията CPUID (1). След RESET сигнал вградени APIC включени, но след това могат да бъдат изключени, след това процесора ще работи периодично като Intel-386/486 (линии LINT0 и LINT1 се използват като NMI # и INTR #, към който може да бъде свързан към контролер 8259A тип прекъсване) ,

Таблица местни вектори (LVT) се състои от шест 32-битови регистри:

прекъсне вектор регистър от таймера;

прекъсване вектор регистър от thermode

прекъсване вектор регистър на монитор на ефективността

LINT0 прекъсне вектор регистър;

LINT1 прекъсне вектор регистър;

Грешка Прекъсване вектор регистър.

Стойностите в тези регистри са определени:

прекъсне вектор номер;

тип капан (фиксиран - прекъсване на вектора, SMI - капан, промяна в режима на системата за управление на, НИМ - НИМ, INIT - изчисти, ExtINT - външно прекъсване: при получаване на заявка за прекъсване на процесора генерира INTA цикъл и чака за номера на прекъсване вектор от външен контролер;

прекъсват маска (прекъсване може да бъде маскирана).

Тези регистри също отразяват състоянието на прекъсване (ако се доставя до сърцевината на прекъсване на процесора в момента).

Освен това, APIC включва таймер регистрира APIC, версия регистър, регистър грешка, регистрите, свързани с услугата прекъсване (регистър заявка приоритет IRR регистър, ISR за поддръжка регистър) и регистри, свързани с предаване и приемане на сигнали IPI.

APIC контролер е предназначен предимно за симетричен multiprotsesornyh система (SMP), описано в Intel «многопроцесорни Спецификация» документ (MPS). Тук симетрия се разглежда в два аспекта:

симетрия памет - всички процесора с обща памет, работа с едно копие на операционната система;

I / O симетрия - всички процесори имат същите входно / изходните устройства и общите прекъсват контролери.

контролер Аз / O APIC е част от чипсета система, например, тя включва хъб и ICH2 ICH3 Intel чипсет. Депутатите spetsifkatsii определено режим обработка три прекъсване:

PIC режим (PIC режим) - емулация двойки PIC 8259A с традиционен сигнализиране прекъсват един процесор (зареждане, BSP Bootstrap Pro cessor) чрез линии INTR и NMI;

Rrezhim работа емисия прекъсне сигнали на местния автобус APIC. Така I / O APIC може да работи заедно с PIC 8259A, предоставяща допълнителни характеристики (по-специално, допълнителни входове IRQ);

Режим, когато устройството генерира прекъсване от I / O APIC; прекъсне може да бъде доставен всеки процесор; всяко искане вход индивидуално програмирани чрез прекъсване таблица за пренасочване (I / O пренасочване Таблица).

Първите два режима осигуряват пълна съвместимост с PC система за прекъсване / AT, те са равностойни на точката софтуер оглед на това, разликите са в областта на дизайн схема. Чрез хардуер нулиране или когато електроенергийната система започва да работи в един от тези режими. Когато системата е готова за прехода в режим на многопроцесорни (MP), APIC се превежда като един балансиран режим и активира прекъсване пренасочване на маса (по-рано инициализира програмно).

Таблица описания на неговите компоненти присъства в MP-система. За да прекъснете тази система трапезни описания включват всички I / O APIC и обработва всички задачи, използвани за прекъсване източници, свързани с I / O APIC и местно APIC. е определен дескриптор дестинация за всеки прекъсване източник:

Прекъсване Тип: вектор с вектор предаване чрез APIC, векторът с вектор външната трансфер (от PIC 8259A), NMI и SMI;

сигнал полярност и тип (или ниво разлика);

идентификатор автобус, в който се намира на източника;

идентификатор искане в автобуса;

APIC име и номера на входа, че е свързан с това искане.

За симетрични системи многопроцесорни в вектори приемлива 10h-FEh диапазон. приоритет Ниво прекъсване вектор се определя от неговия номер, разделен на 16. Най-високото ниво приоритет - нула.

Информация за "Организация на прекъсването и директен достъп до паметта компютърните системи, разпределението на ресурсите, Plug технологии и играя»